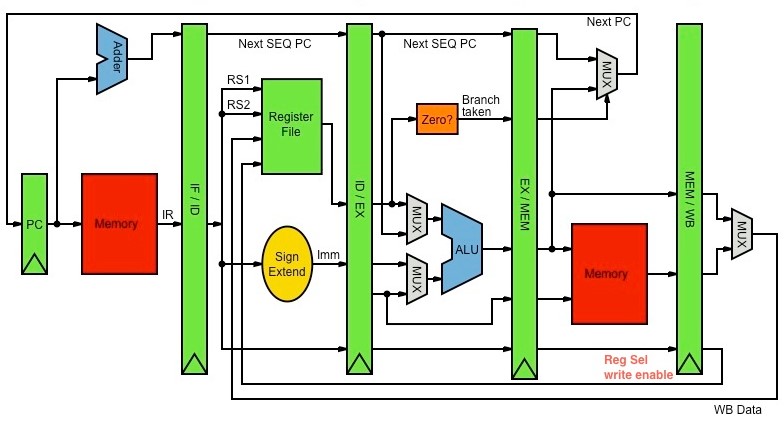

5 Stage Pipelined MIPS Processor

Project Description:

In this project, we designed a working 16-bit, 5 stage pipelined MIPS processor able to execute simple instructions (load word, store word, jump, branch, r-type). All data lines are 8 bits, while instructions are 32 bits. Data forwarding and pipeline stalls are implemented.

Project Github:

View Github Repo

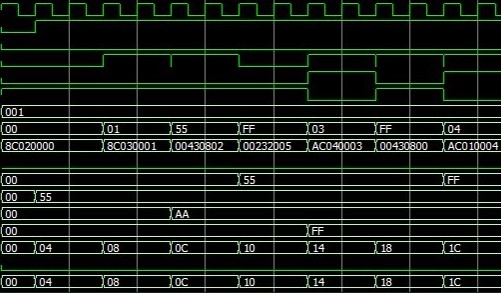

Single-Cycle MIPS Processor

Project Description:

In this project, we designed a working 16-bit single-cycle MIPS processor able to execute simple instructions (load word, store word, jump, branch, r-type). All data lines are 8 bits, while instructions are 32 bits.

Project Github:

View Github Repo

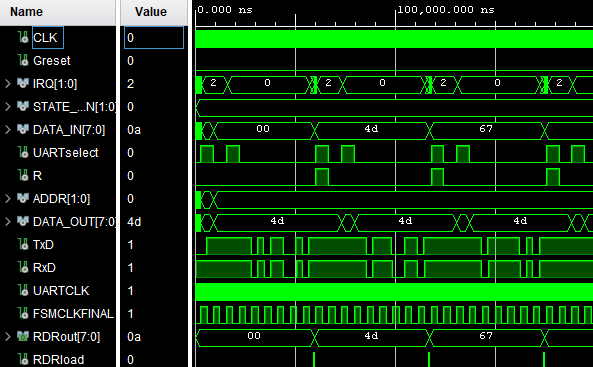

UART Design for Traffic Light Controller

Project Description:

In this project, a UART was designed in structural VHDL to allow for a traffic light controller to communicate debug messages through a serial port.

A full project report which includes schematics, waveforms and more is available in the project repo.

Project Github:

View Github Repo